# plerow<sup>™</sup> APLS1595-R PLL Synthesizer Module

#### Description

The plerow<sup>™</sup> PLL synthesizer module was designed for use in wireless and wireline systems in a wide range of frequency from 50 MHz to 6 GHz. ASB's PLL provides exceptionally low spurious and phase noise performance with fast locking time and low current consumption. All products are available in a surface-mount type package.

#### **Specifications**

| Parameter                 | Unit   | Min.                | Typical | Max. |

|---------------------------|--------|---------------------|---------|------|

| Frequency Range           | MHz    |                     | 1595    |      |

| Output Power              | dBm    |                     | 3       |      |

| Supply Voltage            | V      |                     | 5       |      |

| Current Consumption       | mA     |                     | 30      |      |

| 2 <sup>nd</sup> Harmonics | dBc    |                     | -25     |      |

| Spurious Level            | dBc    |                     | -65     |      |

| Reference Frequency       | MHz    |                     | 10      |      |

| Reference Input Level     | dBm    |                     | 0       |      |

| Phase Noise (C / N)       |        |                     |         |      |

| @ 1 kHz                   |        |                     | -78     |      |

| @ 10 kHz                  | dBc/Hz |                     | -100    |      |

| @ 100 kHz                 |        |                     | -118    |      |

| Output Impedance          | Ω      |                     | 50      |      |

| Operating Temp. Range     | °C     | -40                 | 25      | 85   |

| Package Type & Size       | mm     | SMT, 12.7W×12.7L×3H |         |      |

## **More Information**

Website: www.asb.co.kr E-mail: sales@asb.co.kr

Tel: (82) 42-528-7220 Fax: (82) 42-528-7222

ASB Inc., 44-14, Techno 10-ro, Yuseong-gu Daejeon, 305-510, Korea

1) Measurement conditions are as follows: T =  $25^{\circ}$ C, V<sub>CC</sub> = 5 V, Freq. = 1595 MHz, 50 ohm system.

2) The phase noise tolerance could be within +/- 2 dBc/Hz depending upon the noise applied to PLL from the dc power supplier.

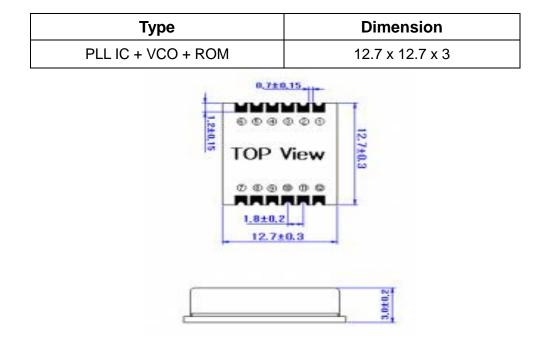

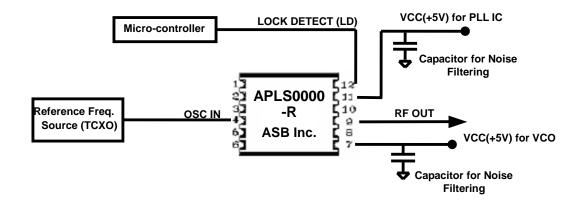

## **Outline Drawing**

| Pin Out for PLL                            |             |         |             |  |  |  |

|--------------------------------------------|-------------|---------|-------------|--|--|--|

| Pin No.                                    | Application | Pin No. | Application |  |  |  |

| 1                                          | GROUND      | 7       | VCC (VCO)   |  |  |  |

| 2                                          | GROUND      | 9       | RF OUT      |  |  |  |

| 3                                          | GROUND      | 11      | VCC (PLL)   |  |  |  |

| 4                                          | OSC IN      | 12      | LOCK DETECT |  |  |  |

| All other Pins are Grounded / Internal ROM |             |         |             |  |  |  |

Copyright ©2006-2017 ASB Inc. All rights reserved. Datasheet subject to change without notice. ASB assumes no responsibility for any errors which may appear in this datasheet. No part of the datasheet may be copied or reproduced in any form or by any means without the prior written consent of ASB.